空间和防务领域,既是FPGA最擅长的应用市场,最难以被ASIC替代的细分行业。

按照欧空局十年前发布的IC设计趋势报告,包括科学探测、星际探索、对地观测、通信导航等在内的数据处理功能,FPGA不可或缺。

“交通工具”偏执狂埃隆·马斯克在上月公开发布其火星计划,并预期20年内实现星际移民,如能成行,为人类率先开启探测之旅的系列火星车,同样居功甚伟。

从最早的探路者号(Mars PathFinder),到国内近年的祝融号,数十年来持续进行中。

英雄人物的出现,更多体现在加速既有进程。

火星车项目作为FPGA在航天领域开山之作,也是最著名的应用案例之一,自然出现在赛灵思为庆祝公司成立25周年时特别出版的专刊。

当期所选20个最具代表性的客户创新案例,航天领域占有三席。

从关键组件到主处理器

Source: Customer Innovation, Xcell Journal 2010

2004年发射的火星车,再加上2009年后在系列重大航天任务,屡立战功的空间高性能计算机SpaceCube。

对可靠性、安全性要求极高的航天工程应用,也可能是除了EDA硬件辅助行业之外,FPGA最能打的细分行业。

后者的IC物理原型验证服务,高性能FPGA更是神龙教主,一统江湖。

目前所有叫得上名号的EDA企业,都有以赛灵思FPGA提供的仿真加速服务。

2019年被新思科技收购的DINI公司,当期榜上有名。

Source: Customer Innovation, Xcell Journal 2010

尽管一直走在异构计算、硬件加速最前沿,代表FPGA最先进调试验证能力,但长期以来,EDA硬件辅助验证的两大行业产品,长期泾渭分明。

2015年,Dini公司研发第一款最基础可观测工具DN Readbacker;与次年新思科技推出HAPS80时高调推出的全局状态可视化GSV(Global State Visibility),功能类似。

技术上源于赛灵思。

都是器件厂商为旗下芯片配提供的数据回读捕获技术,即原有Readback功能的别名或者二次创新开发。

简单说,就是不用加探针,就能看全部信号。

同样的可观测能力(Debugging&Visibility),早在2003年时,以Zebu为代表的现代硬件仿真平台,得到成熟应用。

被称为动态探针Dynamic Probe,与软件行业在开发中用来排查和调试性能问题时采用的动态追踪Dynamic Tracing类似。

区别于芯片厂商提供片上逻辑分析仪(赛灵思ILA等)的静态探针Static Probe,这是所有工程师熟练应用的板级调试手段,也是所有器件厂商为用户提供的必备工具。

如果寻源的话,所谓动态探针技术,甚至可追溯到行业鼻祖Quickturn公司。

其在1988年推出Rapid Prototype Machine,用赛灵思XC3090商用FPGA构建的行业开山之作。也是芯片设计行业进入到超大规模IC时代后,第一款真正意义上的现代仿真加速器。

EDA硬件辅助验证仿真加速的三十年进化史

Source: Hardware Emulation-Three Decades of Evolution, Rizzatti, 2015

对设计进行在线调试的芯片可观测能力,现在成为各大EDA厂商,为用户提供硬件辅助验证服务的标配。

硬件仿真(Emulation)与IC物理原型验证,作为ASIC设计硅前验证流程中两大必经环节,各有专长,但彼此之间就像是楚河汉界。

2021年,EDA巨头更进一步,新思科技推出首款融合两大仿真加速功能的Zebu EP1,既是传统的Emulation,也可切换到Prototype。

2022年,国内芯华章也推出旗下的HuaPro P2E,产品设计理念与之类似。

尽管FPGA应用设计和ASIC有着相同的设计开发流程,时至今日,EDA硬件辅助验证工具,仍主要只面向ASIC设计提供服务。

始终与FPGA应用设计距离遥远。

FPGA和ASIC拥有同样的调试验证流程

从EDA供应商角度,也有些大炮打蚊子的意思,杀鸡焉用牛刀。

具体到实际应用层面,每一代最新推出的两大行业工具,都主要使用赛灵思最新、规模最大的高端器件。

配套的调试验证软件,只与特定型号的器件绑定使用。

从终端用户视角,即便抛开价格因素,也不太用不上。

既然ASIC芯片设计的前端验证,与FPGA应用开发的在线调试,都是直接在FPGA硬件上完成,那为什么同样的技术,后者不能享有呢?

在大多数场景下,更快,总是更好的。

痛感神经发达的NASA

EDA工具是降低经验门槛,减少不确定性风险利器。

既有的行业惯性思维中,高大上的电子设计自动化工具,为用户提供的“发现问题,影响域分析,以及改进建议”的三板斧。

着力在设计源码和网表级别。

即国内所称的可编程逻辑器件软件,如7年前正式实施的测试国标GB/T 33783-2017等。

虽然FPGA能够像软件一样“编程”使用,甚至可以对电路功能进行在线升级和更新(如赛灵思的动态功能交换DFX等)。但作为芯片本身,其内部信号完全是不可见的。

以01二进制数据集合而成的位流,更是用户设计成果体现,承载了定制电路的若干创新。

既是数字逻辑世界(RTL&Netlist)和芯片物理世界(Hardware)的之间分界线,也是解决复杂系统耦合关系的切入点。

FPGA应用开发过程中的在线调试,经验丰富的硬件工程师,通常能熟练驾驭,所以很难成为症状明显的所谓“行业痛点”。

即便有问题,重新编程再次配置就行了,不会像芯片设计那样,必须面对成本高昂的“流片失败”风险。

翻译过来,大概是FPGA不需要像ASIC那样“严格”仿真过程。

FPGA应用开发和ASIC芯片设计,毕竟是不同行业的两码事。

像硬件仿真平台Zebu,帮助用户尽可能实现Zero Bug,在设计阶段就追求零缺陷目标,对于FPGA应用设计而言,就像过高精度追求。

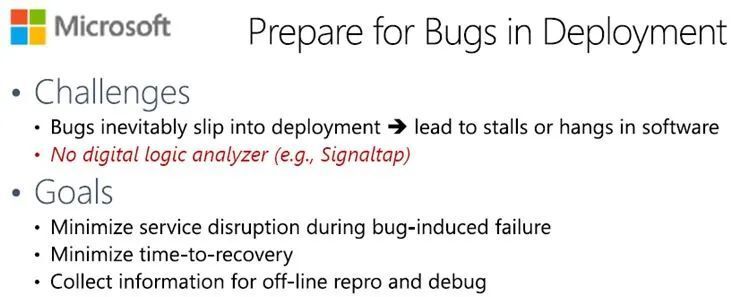

只有像微软这样的科技巨擘,因为需要考虑到FPGA系统的可用性问题,才会偶有痛感。但FPGA在数据中心的加速计算,又没有像预期那样成为绝对主流。

Source: Requirements for Deploying and Developing for FPGAs, Microsoft research, FPGA16

在计算机领域,不管是设计(Dev)还是运维(Ops),如果某个系统内部是“不可见”,那么就距离崩溃不远了。

对于FPGA行业更普遍的观点是,即便开发阶段可能隐藏的设计Bug,就算逃逸到部署阶段,影响了系统可靠性问题,乃至损害可用性,也似乎更多归结为只是后期的运维问题。

类似理念和观点,不乏EDA行业大佬。

2015年,在业界著名的设计验证DVCON研讨会,DINI Group公司创始人在其与会的专题演讲中,将两者之间的关系,更像是同一套“设计方法学”上的两个分支。

Source: FPGA Debug Using Configuration Readback, DVCON 2015, Mike Dini

FPGA应用开发的验证难题,并不等同于ASIC设计的调试困境。

但对于NASA这样的机构用户,现有的常规调试验证手段,远远不够。想要真正确保FPGA应用开发质量,得像ASIC硅前验证那样严格。

尽可能与“流片”一样可靠,才能真正保障应用开发的设计质量。

作为空间系统中的关键组件,FPGA芯片自身的技术进步,其容量规模、复杂度持续增长,对复杂的软/硬件系统进行验证,变得非常耗时。

已经与ASIC验证要求近乎无差别。

2008年时,NASA的火星探测器平台(MER,Mars Exploration Rovers),使用的高可靠FPGA,硬件规模仅为32K 等效逻辑门;

但即便对于一个典型的FPGA应用设计,验证时间可能也长达3个月。

载荷(MSL, Mars Science Laboratory)所使用的高性能FPGA,硬件容量已经更是达到200万门,只有创新的EDA工具,才能真正提升设计开发效率。

更快,更高效,才能更好确认设计成果。

既然现有的EDA硬件辅助服务指望不上,那就从实际工程中所感受的“痛点”出发,启动FVAX(FPGA Verification Accelerator)项目。

加速设计左移,节省成本支出

Source: MAPLD 2008, Jane Oh and Gary Burke

如果说软件仿真就像画素描,板级调试验证则有着“3D克隆”效果。硬件电路在FPGA板卡上全速运行,与连接的传感器、作动器直接交互。

软件仿真作为FPGA调试验证的入口,可观测能力最好,通常能够解决大部分显而易见的设计问题。

但运行速度很慢,很难实现完整的功能覆盖、代码覆盖。

测试程序的开发、与FPGA应用设计可能由同一个工程师完成,手工创建的仿真测试程序本身可能存在问题。

并且在仿真过程中,很难对系统与外部环境的实时交互,以及异步处理行为进行建模。

上述诸多因素,都可能导致那些隐藏的设计错误,从仿真阶段逃逸到板级调试阶段,将不可避免。

在板级调试阶段,工程师通常使用芯片厂商提供的免费内嵌式逻辑分析仪,比如赛灵思当时的ChipScope,获得有限的信号观测能力,或者把目标信号引到未使用的芯片管脚上,用示波器/逻辑分析仪进行观测。

现有方法,使那些只在特定运行情况或者长时间运行后出现的问题,很难通过设置触发条件的方式,重现故障场景。

尽管EDA硬件辅助验证行业的先进调试验证软件,使用户能够获得良好的信号可观测能力和可控性。

但是,不支持特定型号之外的其它FPGA器件,更不支持用户自己的定制板卡和产品原型。

虽然很先进,但是用不上。

想高效验证,工具得先行。

那就再造适合FPGA应用开发的创新工具,可应用于任何FPGA,任意板卡的调试验证工具。

Source: MAPLD 2008, Jane Oh and Gary Burke

在NASA看来,实现预期的验证加速,主要取决于两个关键要素:

能够支持任意FPGA芯片。

可通过标准的测试接口,适配任意FPGA板卡。

具备对FPGA内部信号的全面可观测能力,还提供便捷的用户接口,观察实际运行状态是否与预期相符;

并且,就像软件的单步调试一样,能够看到电路的在线运行过程,加快调试工作进程。

就像EDA硬件辅助验证行业两大工具的复合体,既有高性能原型验证系统的精髓,也有更高端硬件仿真的影子。

Source: MAPLD 2008, Jane Oh and Gary Burke

如果抛开FPGA硬件容量大小,NASA的这一步,比擅长于SoC验证的硬件仿真,与2003年EVE公司推出第一款产品相比,也只是稍晚了5年。

仅从调试验证软件的先进程度,比EDA厂商的原型验证服务领先8年。

从同行的角度,比空客的航天和防务公司,领先了大约15年。

在欧空局FPGA专题研讨会的公开信息,2023年直接采用西门子的原型验证平台,对多FPGAs的复杂系统进行仿真加速验证。

效率提升了60倍。

此前2016年,航天领域排名第一的FPGA厂商,也推出全新调试工具。

Source: Spatial Debug & Debug without re-programming in Microsemi FPGAs, 2016

同样是FPGA运行时的信号可观测能力(Observability),以及运行的强制赋值在线改写01数值(Controllability)。

与EDA硬件辅助验证服务,从数年前的高端专用,到现在已成基本配置的FPGA可观测性能力(Full Visibility&Debugging),异曲同工。

一个在赛灵思的FPGA完成,而Microsemi的调试工具,则是专用于旗下芯片。

空客航天和防务的部分FPGA型号

Source: FPGA development in Airbus products,2023

从2021年后,该工具更新迭代速度明显加快,从最初的只适用SmartFusion2,现在已扩展到支持旗下的全系列FPGA。

为包括航天行业在内的所有用户,提供调试验证服务。

相当于FVAX项目平移的“产品化”落地。

行运一条龙

NASA启动的仿真加速项目,就像是FPGA高可靠设计在原有的测试验证全流程的强化,补上了关键一环。

对以赛灵思为代表的高性能器件,更是有着画龙点睛的效果。

1998年,人类社会从后工业进入信息化时代。同年赛灵思公司正式推出其首款Virtex系列高性能芯片,从此开启登上行业龙头的进阶之旅。

市场上的大获成功,除了表现在EDA硬件辅助验证行业,仿真加速市场应用一枝独秀之外,也开始在航天市场发力。

稳居行业第二。

Source: Xilinx Analyst Day,2017

所有的数字芯片,都会存在软错误或软失效。

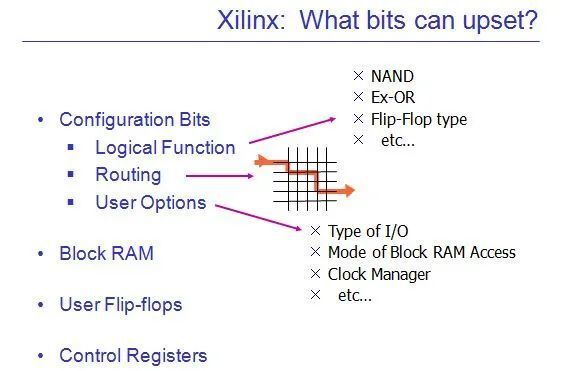

对于高性能FPGA芯片,由配置存储器决定电路结构及功能的硬件编程方式,还需要额外关注配置存储器中的0/1数据,即Configuration Bits。

因受单粒子效应影响被动发生改变,可能引发的系统异常。

恶劣运行环境的空间应用,如果处理不当,就会伤筋动骨。

Source: MAPLD 2003, Gary Swift etal.

对于器件厂商,为用户提供SEU Controller支持,成为基本配置。

2000年,为了更好应对器件在空间环境下的运行使用,赛灵思联合NASA推进器试验室JPL,建立单粒子效应联盟(Single-Event Effects Consortium, SEEC)。

两年后,将其进一步升级为辐照测试联盟(Xilinx Radiation Test Consortium,XRTC),面向境内成员单位开放的商业化组织,共同研发和使用大型故障注入测试设备(Fault Injection Infrastructure)。

有了这样的大杀器作保障,从此开启SRAM FPGA在航天领域的开挂之旅。

大型故障注入测试设备,成为诸多重大航天工程项目的基石。

这就包括曾入选赛灵思客户创新案例,屡获NASA创新大奖的空间高性能计算机SpaceCube。

通过在系统架构设计、软件设计层面进行加固,使得普通的商用级FPGA,也能胜任空间任务。

包括2009年使用商用级FPGA,提供关键交汇对接信号,完成哈勃望远镜的维修任务。

如果使用传统的航天专用抗辐射计算机,完成同样的工作,需要多达25台。

即便在“不计成本保可靠性”的航天1.0时代,在满足成本和可靠性要求的同时,提升数据处理效能。

FPGA空间高性能计算机的成名作

从2003年火星车项目,XRTC开始扬名立万,现已成为诸多重大航天工程项目的基石。

测试验证的FPGA芯片类型,除了宇航级,也包括商用级。

空间高性能计算机使用的FPGA芯片型号

来源:根据公开资料汇总整理,复及科技,2020

XRTC的两大核心组件,提供SEU仿真能力的配置位流故障注入工具,以及用于破坏性测试的辐照试验模块。

使命定位为帮助境内联盟成员更高效进行系统调试,解决FPGA应用设计和产品开发中的问题。

毕竟,不管是作为主处理器,还是核心关键组件使用,FPGA是出了名的设计开发难度大,对大容量芯片的测试验证难度及所需工作量,随之同步增加。

再加上软件在内,软硬件紧密耦合的复杂系统,更是难上加难。

发挥的经济价值包括:

分摊昂贵的测试成本

系列FPGA待测器件往往异常复杂,特别是军用Q系列、宇航级QR,代价高昂

为不同领域的联盟成员引入专家和培养人才

随着大容量、高性能FPGA设计更为复杂,测试难度随之增大

为航天航空、防务领域提供应用设计和工程实现等支持

帮助客户应用最佳实践,更高效地调试,解决问题并加强客户对 Xilinx 技术的理解

赛灵思公司在2011年发布的年度质量报告显示,该设备已服务的境内联盟成员单位数量,超过100家。

尽管功能强大,但对包括像雷神公司这样不差钱的终端用户,还是过于厚重。

特别是作为行业黄金法则的辐照试验,价格昂贵不说,每次需要花费数月进行准备。

一旦失败,付出的时间成本、经济成本不菲。

由此以XRTC作为参考基石,研发更轻量的故障注入测试软件。

在工程实用性方面,并非作为项目性质的概念验证框架。而是既能服务日常的应用设计开发,也能与辐照实验无缝融合。

Source: Patrick Fleming and Bill Rowe,Raython Technologies,2020

目的是提供解决方案,轻量化,成本更低。

具有快速,高效,且测试粒度更精细等特点。

并且,与其它行业不同,由器件厂商提供给用户使用的内嵌测试电路(比如,赛灵思SEU Mitigation IP核),在空间应用场景,用户大多是采用外部监测和刷新(Scrubbers)。

所以轻量便捷的故障注入测试软件,对用户待测FPGA设计的性能、资源使用不会有任何影响。

在应用设计过程中,通过故障注入测试,减少“过度防护”带来的性能损失,成本开销,在FPGA可靠性、运行效能、设计成本三者之间进行权衡。

使用更方便,并且成本更低。

Source: Using Fault Injection for Characterization of SEU Mitigated FPGA Designs, Raython, 2020

从大型专用设备,昂贵复杂的硬件平台,向轻量级进化,已经渐成趋势。

雷神技术的故障注入软件,与欧空局推荐使用的FT-UNSHADES2相比,更进一步。

只提供软件,跨硬件平台实施的通用方案。

FT-UNSHADES2与美国的大型专用设备XRTC相比,除了更小型轻量之外,还额外扩展了故障注入的位流数据类型。

Source: Hipólito,FT-Unshades2 overview,2019

从最早的仿真加速功能起步,主要服务航天ASIC设计制造的前端验证。

增加FPGA应用开发专用的SEU测试功能,即FPGA模式。

前者是2008年美国航天航空管理局(NASA)FVAX项目的欧洲本地化,后者则是XRTC设备的欧洲平替版。

也可以将其视为EDA硬件辅助验证最早的跨界服务。

FPGA作为平民版ASIC,既是创新,也是应有之义。

流水不争先

航天高端俱乐部,迎来新成员。

商业航天来临,包括低轨卫星组群概念等,为整个FPGA应用市场注入全新的增长动力。

作为电子设备中的关键组件,FPGA芯片能够快速定制为用户所需的功能,抛开硬件规模大小,芯片出货量最大的莱迪思,2022年宣布进军航天市场。

在赛灵思和Microsemi两强中开创新市场。

相比ASIC芯片,FPGA在空间电子设备中的占比逐年增加。以欧空局的哨兵2号卫星为例,使用的249个芯片中,就有149片是FPGA,占比超过50%。

Source: ESA strategy ASIC & FPGA for space,2013

莱迪思目标是商业航天,特别是低轨卫星的数据处理。

选择的合作伙伴大有来头,前身是英国第三大防务公司Cobham的先进航天电子部门CAES,2023年被PE资本收购并以FrontGrade品牌开展业务。

将中小规模FPGA在空间市场机遇的定位为,目前市场上两强的大芯片要么过“大”,显得“浪费”;小芯片的性能,又太拉垮。

从用户成本角度看,那些“不大不小刚刚好”FPGA,正合适。

除了性能因素,尚需综合考虑面积(Size)、重量(Weight)、功耗(Power)和成本(Cost),即SWaP-C。

Next-Gen FPGA for Space, David Meyouhas, 2023

FrontGrade的股东虽然不为大众熟知,Veritas资本作为全球最大的政府服务基金,主要投资于那些为政府和商业客户提供关键产品、软件和服务的科技公司。

从2012年以来,已经实现20倍的增长,目前管理400亿美元资产。

在大多数投资机构认为很难接受和融入、认为“难搞”的政府环境,深耕数十年,即便经历了互联网、移动互联网时代的投资繁荣期,始终未被诱惑,越出投资边界。

其创始人也被高盛CEO称为“低调,靠实干产生了巨大的影响力”。

这至少已经是Veritas资本涉及的第二家与FPGA业务相关的公司了。

2015年时,收购拥有航天与防务、以及政府业务的Alion公司。三年后,又以该公司为主体,收购MacB公司,后者聚焦政府和防务领域信息安全,也是美国“可信微电子计划”的主要参与者之一。

全球独有的FPGA位流安全解决方案,其中也包括航天领域单粒子效应的测试验证。

与MacB公司的位流分析工具,在空间应用服务,占比较小不同。

FrontGrade的航天器件可靠性业务,几乎参与了欧美所有重要的航天工程,包括1969年阿波罗11号以来的每一次载人航天任务。

莱迪思也成为继赛灵思、Microsemi两大厂商之后,FrontGrade合作的第三家FPGA厂商。

软件和EDA巨头新思合作,硬件有行业元老加持,谋定而动,对空间市场前景抱以厚望。

从芯片厂商的视角,在器件架构、制造工艺上进行加固,在FPGA的整个应用生命周期中,只是起点。

用户使用EDA开发软件,在硬件设计上通过多模冗余以及抗辐加固手段,如ECC、CRC等,以尽可能实现预期的可靠性和可用性需求,更多着力在设计流程。

从终端用户的角度,对于包括莱迪思在内的新进入者来说,至少从赛灵思既有的成功历程,可能还不够。

“Trust, But Verify”,可以信任,但需要验证,是美国前总统里根在1987年时,对美苏两个超级大国之间竞合关系的高度概括。

对于FPGA的功能安全挑战,包括空间的恶劣运行场景,同样适用。

按照赛灵思公司从1998年以来的成功实践,即便芯片在器件层面可靠性只是差强人意,但如果能够在短时间内修复,仍可能达到预期设计目标。

2023年10月11日,在大盘微幅上涨,紫光国微和复旦微两家涉军题材的FPGA公司,反而逆势下跌,与其它军工股一道回调。

当天全网乱飞的“小作文”中,就包含“电子产品经分级评估后使用,没必要用军用级的就改用消费级”之类的市场传闻。

从昂贵的专用,到更具性价比的通用,均是成本因素。

既有直接使用XC4VFX60 FPGA打造的空间高性能计算机(SpaceCube),也有性价比商用现货Spartan6,被欧洲巨头空客的航天和防务部门用作空间产品的关键组件。

如果要找一个对FPGA功能安全需求,与空间应用最接近的行业作为平替备选的话,汽车电子无疑将排名居前。

进入到智能汽车时代,后者作为众多FPGA厂商的芯战场。

那么在商业航天快速推进的今天,空间会成为应许之地吗?

对于关键且重要的行业用户,需要做的是更经济易用的调试验证。

全文完,感谢您的耐心阅读。